This Page Is Inserted by IFW Operations and is not a part of the Official Record

# **BEST AVAILABLE IMAGES**

Defective images within this document are accurate representations of the original documents submitted by the applicant.

Defects in the images may include (but are not limited to):

- BLACK BORDERS

- TEXT CUT OFF AT TOP, BOTTOM OR SIDES

- FADED TEXT

- ILLEGIBLE TEXT

- SKEWED/SLANTED IMAGES

- COLORED PHOTOS

- BLACK OR VERY BLACK AND WHITE DARK PHOTOS

- GRAY SCALE DOCUMENTS

## **IMAGES ARE BEST AVAILABLE COPY.**

As rescanning documents *will not* correct images, please do not report the images to the Image Problem Mailbox.

Abstract (Basic): JP 7235177 A

The semiconductor memory has a memory cell array (Sal-San) provided with a number of memory cells. The row and column address signals (RAS,CAS) are provided with in set time. A refreshing circuit (7A) refreshes the memory cells. The main part is energized using high potential and low potential power supplier (VDD, VSS), and the necessary power supply is selected using a mode detector (11A).

The mode detector is operated by a special refreshing circuit (12). An operating power supply (VOSC) operates based on the two power supplies. A main power circuit (23) operates the special refreshing circuit. Starting devices (11A, 22) are provided to start the main program to control the operations of all the power supplies.

**JUL 23** 2003 m

TECHNOLOGY CENTER 2800

(11)特許出願公開番号

#### (19)日本国特許庁(JP)

(12) 公開特許公報(A)

### 特開平7-235177

(43)公開日 平成7年(1995)9月5日

| (51) Int.Cl. <sup>6</sup> | 識別記号 | 庁内整理番号 | FI         | 技術表示箇所 |

|---------------------------|------|--------|------------|--------|

| G11C 11/403               |      |        | G11C 11/34 | 363 M  |

#### 審査請求 未請求 請求項の数2 OL (全 9 頁)

| (21)出顧番号 | 特顯平6-25653      | (71)出顧人 | 000005223            |

|----------|-----------------|---------|----------------------|

|          |                 |         | 富士通株式会社              |

| (22)出顧日  | 平成6年(1994)2月23日 |         | 神奈川県川崎市中原区上小田中1015番地 |

|          |                 | (71)出願人 | 000237617            |

|          |                 |         | 富士通ヴィエルエスアイ株式会社      |

|          |                 |         | 愛知県春日井市高蔵寺町2丁目1844番2 |

|          |                 | (72)発明者 | 小川和樹                 |

|          |                 |         | 愛知県春日井市高蔵寺町二丁目1844番2 |

|          |                 |         | 富士通ヴィエルエスアイ株式会社内     |

|          |                 | (74)代理人 |                      |

|          |                 |         |                      |

|          |                 |         |                      |

|          |                 |         |                      |

#### (54)【発明の名称】 半導体記憶装置

(57)【要約】

【目的】セルフリフレッシュ動作のみに関係する回路 を、その動作に間に合うように動作させ、消費電流を低 減できる半導体記憶装置を提供する。

【構成】セルフリフレッシュ回路7Aは検出回路11 A、オシレータ12、ラッチ22及び電源回路23を備 える。検出回路11Aはコラム信号バーCASの立ち下 がりに続くロウ信号バーRASの立ち下がりから検出時 間経過後に検出信号REを出力し、検出時間より短い設 定時間経過後に活性化信号GEを出力する。ラッチ22 は信号バーRASがLレベルで信号GEがHレベルにな ると、起動信号バーSTを出力する。電源回路23は起 動信号バーSTに基づいて、電源VDDに基づく電源Vos cを出力する。オシレータ12は信号REに基づいて活 性化され、電源Voscに基づいてクロック信号ADDC LKを出力する。

#### 本発明を具体化した一実施例の半導体記憶装置の電気的結成を示すプロック目

#### 【特許請求の範囲】

【請求項1】 複数のメモリセルを備えたメモリセルア レイ(Sa1~San)と、

コラムアドレスストローブ信号(パーCAS)の立ち下 がりに続くロウアドレスストローブ信号(パーRAS) の立ち下がりを基準として所定の検出時間が経過したと き、前記メモリセルアレイ(Sa1~San)のメモリ セルのセルフリフレッシュを行うセルフリフレッシュ回 路(7A)とを備え、高電位電源(VDD)及び低電位電 源(VSS)に基づいて動作する半導体記憶装置におい て、

前記セルフリフレッシュ回路(7A)は、

前記検出時間の経過を検出してセルフリフレッシュ動作 を開始させるためのモード検出回路(11A)と、 前記モード検出回路によって動作が開始され、かつ、セ

ルフリフレッシュ動作のみに関係する動作を行うセルフ リフレッシュ専用回路(12)と、

前記高電位電源(VDD)及び低電位電源(VSS)に基づ く動作電源(Vosc)を前記セルフリフレッシュ専用回 路(12)に供給するための電源回路(23)と、

前記検出時間よりも短い設定時間の経過を検出したと き、前記高電位電源(VDD)及び低電位電源(VSS)間 に前記電源回路(23)を接続して該電源回路(23) に電流を流し、前記動作電源(Vosc)を出力させるた めの起動手段(11A, 22)とを備える半導体記憶装 置。

【請求項2】 前記セルフリフレッシュ専用回路は、前 記メモリセルアレイ (Sal~San)のメモリセルを 選択する内部アドレスを発生させるためのクロック信号 を発生するオシレータ (12)であり、

前記電源回路(23)は前記高電位電源(VDD)及び低 電位電源(VSS)間に直列に接続された第1及び第2の トランジスタ(31,32)からなり、少なくとも前記 第1のトランジスタ(31)は前記起動手段によって導 通され、前記第1及び第2のトランジスタ(31,3 2)間から前記動作電源(Vosc)を出力するように構 成した請求項1に記載の半導体記憶装置。

【発明の詳細な説明】

[0001]

【産業上の利用分野】本発明は半導体記憶装置に係り、 詳しくはダイナミック・ランダム・アクセス・メモリ

(以下、DRAMという)のセルフリフレッシュに関す る。

【0002】近年の半導体技術の進歩により、DRAM の記憶容量は益々増大し、DRAM自体の消費電流も増 大しつつある。しかし、市場の要求はより消費電流の少 ないものへと傾いている。この市場要求を満たすため、 必要以上に回路を動作させることを避け、消費電流を少 なくする必要がある。特に、DRAMを使用したシステ ムでは、システムが動作していないとき、バックアップ 用のパッテリ電源によりメモリセルのセルフリフレッシ ュが行われる。このセルフリフレッシュ時の消費電流を 少なくする必要がある。

[0003]

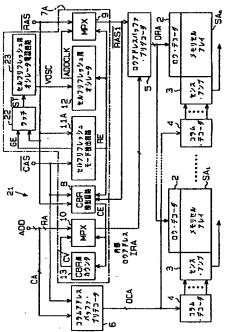

【従来の技術】図4には従来のDRAMの一例が示され ている。このDRAM1は複数のメモリセルアレイSa 1~San、ロウアドレスバッファ・プリデコーダ5、 コラムアドレスバッファ・プリデコーダ6及びセルフリ フレッシュ回路7を備えている。各セルアレイSa1~ Sanは多数のメモリセルよりなる。各セルアレイSA 1~SAn へのデータの書き込み又は読み出しは1ビッ ト単位で同時に行われる。従って、DRAM1にはnビ ットのデータがパラレルで書き込まれる。また、DRA M1からはnビットのデータがパラレルで読み出され る。

【0004】DRAM1にはシステム電源から高電位及 び低電位電源VDD, VSSが供給され、DRAM1は両電 源VDD及びVSSに基づいて動作する。また、DRAM1 には前記システム電源と並列にパックアップ用のバッテ リ(図示略)が接続されている。システム電源が遮断さ れると、バッテリからDRAM1に電源VDD, VSSが供 給され、DRAM1はこの電源VDD, VSSに基づいて動 作する。

【0005】DRAM1には図示しない制御装置からア ドレス信号ADD、ロウアドレスストローブ信号(以 下、単にロウ信号という)バーRAS及びコラムアドレ スストローブ信号(以下、単にコラム信号という)バー CASが入力される。システム電源が遮断された後、コ ラム信号バーCAS及びロウ信号バーRASが所定のタ イミングで入力されると、リフレッシュ回路7によって セルアレイSa1~Sanのメモリセルのセルフリフレ ッシュが行われる。

【0006】セルアレイSA1 ~SAn にはロウデコー ダ2、センスアンプ3及びコラムデコーダ4がそれぞれ 設けられている。各デコーダ2はバッファ・プリデコー ダ5に接続されている。各デコーダ4はバッファ・プリ デコーダ6に接続されている。バッファ・プリデコーダ 6には前記アドレス信号ADDにおけるコラムアドレス 信号CAが入力されるとともに、コラム信号バーCAS が入力される。バッファ・プリデコーダ6はアドレス信 号CAに基づいたプリデコード信号DCAを各デコーダ 4に出力する。

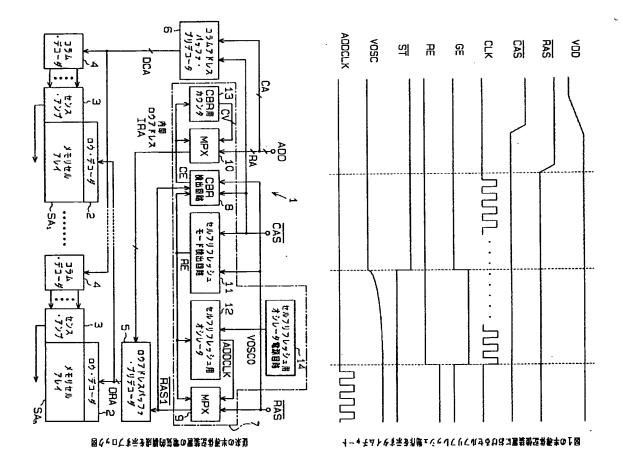

【0007】リフレッシュ回路7は、CBR検出回路 8、マルチプレクサ(以下、MPXという)9,10、 セルフリフレッシュモード検出回路11、セルフリフレ ッシュ用オシレータ12、CBR用カウンタ13及びセ ルフリフレッシュ用のオシレータ電源回路14により構 成されている。

【0008】MPX9にはロウ信号バーRASが入力さ れる。MPX9は前記バッファ・プリデコーダ5に接続 されている。MPX10には前記コラム信号パーCAS が入力される。モード検出回路11及びCBR検出回路 8にはロウ信号パーRAS及びコラム信号パーCASが 入力される。オシレータ12には電源回路14が接続さ れている。

4 1

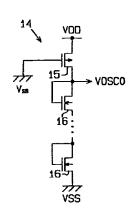

【0009】 電源回路14は図5に示すようにPMOS トランジスタ15及び複数のNMOSトランジスタ16 からなる。トランジスタ15及び複数のトランジスタ1 6は電源VDD及びVSS間に直列に接続されている。トラ ンジスタ15のゲートには電源VSSが印加され、各トラ ンジスタ16のゲートはそのドレインに接続されてい

る。電源回路14はトランジスタ15のドレインから電 源VDDに基づくオシレータ電源Vosc0をオシレータ12 に出力する。従って、図6に示すように、電源VDDが立 ち上がると、電源回路14のトランジスタ15,16が オンし、オシレータ電源Vosc0がほぼ同時に立ち上が る。

【0010】さて、DRAM1にシステム電源が供給さ れた状態において、データの読み出しを行うべく、所定 のタイミングでロウ信号バーRAS及びコラム信号バー CASがDRAM1に入力される。この後、アドレス信 号ADDがDRAM1に入力される。すると、MPX1 0はアドレス信号ADDのロウアドレス信号RAを内部 ロウアドレス信号1RAとしてバッファ・プリデコーダ 5に出力する。

【0011】パッファ・プリデコーダ5はアドレス信号 IRAをプリデコード信号DRAにデコードし、デコー ド信号DRAを各デコーダ2に出力する。各デコーダ2 はデコード信号DRAを選択信号にデコードしその選択 信号に基づいて各セルアレイSA1 ~SAn の所定のワ ード線を選択する。

【0012】一方、バッファ・プリデコーダ6はアドレス信号ADDのコラムアドレス信号CAをプリデコード 信号DCAにデコードし、デコード信号DCAを各デコ ーダ4に出力する。各デコーダ4はプリデコード信号D CAを選択信号にデコードしその選択信号に基づいて各 セルアレイSA1 ~SAn の所定のビット線対を選択す る。

【0013】その結果、各セルアレイSA1 ~SAn で は、選択されたワード線及びビット線対に接続されてい るセルが選択される。選択されたセルのデータは対応す るビット線対を介して読み出される。読み出されたデー タは各センスアンプ3によって増幅され、図示しない出 力回路に転送される。

【0014】さらに、DRAM1にシステム電源が供給 された状態において、CBR検出回路8に所定のタイミ ングでロウ信号バーRAS及びコラム信号バーCASが 入力されると、セルアレイSa1~Sanの通常のリフ レッシュが行われる。

【0015】また、図6に示すように、システム電源に

よって電源VDDが立ち上がると、オシレータ電源Vosc0 はほぼ同時に立ち上がっている。システム電源が遮断さ れると、DRAM1への電源VDDの供給は前記バッテリ によって行われ、電源VDDは立ち上がった状態に保持さ れる。そのため、オシレータ電源Vosc0も立ち上がった 状態に保持される。

【0016】この後、コラム信号パーCASが立ち下が ってからロウ信号パーRASが立ち下がると、モード検 出回路11は内部のクロック信号CLKに基づいて経過 時間を計測する。信号パーCAS及びパーRASがロー レベルのまま100µsec経過すると、モード検出回 路11はセルフリフレッシュを行うべく、Hレベルとな る検出信号REをCBR検出回路8、オシレータ12及 びMPX9に出力する。

【0017】オシレータ12はHレベルの検出信号RE が入力されると活性化され、オシレータ電源Vosc0に基 づいて内部アドレスを発生させるための所定周波数のク ロック信号ADDCLKを出力する。MPX9はクロッ ク信号ADDCLKを入力し、内部信号バーRAS1と してバッファ・プリデコーダ5及びCBR検出回路8に 出力する。

【0018】そして、内部信号バーRAS1の立ち下が りがバッファ・プリデコーダ5に入力されると、バッフ ァ・プリデコーダ5が活性化される。一方、内部信号バ ーRAS1の立ち下がりがCBR検出回路8に入力され ると、CBR検出回路8はカウントアップ信号CEをカ ウンタ13に出力する。

【0019】カウンタ13はカウントアップ信号CEに 基づいてアドレスをアップカウントし、カウント値CV をMPX10に出力する。MPX10はカウント値CV をアドレス信号1RAとしてバッファ・プリデコーダ5 に出力する。

【0020】すると、バッファ・プリデコーダ5はアド レス信号 I RAに基づくプリデコード信号D RAを各デ コーダ2に出力する。各デコーダ2はデコード信号D R Aを選択信号にデコードしその選択信号に基づいて各セ ルアレイSA1 ~ SAn の所定のワード線を選択する。 選択されたワード線に接続されるセルのデータはセンス ・アンプ3によって増幅され、そのデータは再びセルに 書き込まれる。尚、バッファ・プリデコーダ5は内部信 号バーRAS1の立ち上がりが入力されると非活性化さ れる。

【0021】そして、再び内部信号バーRAS1の立ち 下がりがパッファ・プリデコーダ5及びCBR検出回路 8に入力されると、バッファ・プリデコーダ5が活性化 される。また、CBR検出回路8はカウントアップ信号 CEをCBR用カウンタ13に出力する。そのため、C BR用カウンタ13はアドレスを更にアップカウント し、そのカウント値CVをMPX10を介してアドレス 信号1RAとしてパッファ・プリデコーダ5に出力す 【0022】すると、バッファ・プリデコーダ5はアド レス信号IRAに基づいたプリデコード信号DRAを各 デコーダ2に出力する。各デコーダ2はプリデコード信 号DRAを選択信号にデコードしその選択信号に基づい て各セルアレイSA1~SAnの所定のワード線を選択 する。選択されたワード線に接続されるセルのデータは センスアンプ3によって増幅され、そのデータは再びセ ルに書き込まれる。

【0023】以下、オシレータ12から出力される内部 信号パーIRASの立ち下がり毎に、前記と同様にして 各セルアレイSa1~Sanの異なるワード線が順次選 択され、その選択されたワード線に接続されたセルのセ ルフリフレッシュが行われる。

【0024】そして、電源回路14は電源VDDに基づい て所定のレベルのオシレータ電源Vosc0を出力するまで に、所定の時間を要する。オシレータ電源Vosc0が所定 のレベルに達する以前に検出信号REが入力されると、 クロック信号ADDCLKの周波数が所定の周波数より も低くなってしまう。そのため、電源VDDがHレベルで あると、すべてのトランジスタ15,16がオンし、常 時オシレータ電源Vosc0を出力する。トランジスタ1 5,16のオンに基づいて電源VDD,VSS間には常時電

流が流れ、電流が消費される。

[0025]

【発明が解決しようとする課題】従って、上記DRAM 1ではセルアレイSa1~Sanをセルフリフレッシュ しない場合にも電源回路14が電流を消費し、消費電流 が増大していた。

【0026】本発明は上記問題点を解決するためになさ れたものであって、その目的は、セルフリフレッシュ動 作のみに関係する回路を、セルフリフレッシュ動作に間 に合うように動作させることにより、消費電流を低減で きる半導体記憶装置を提供することにある。

[0027]

【課題を解決するための手段】上記の目的を達成するた め、本発明では、検出時間の経過を検出してセルフリフ レッシュ動作を開始させるためのモード検出回路と、モ ード検出回路によって動作が開始され、かつ、セルフリ フレッシュ動作のみに関係する動作を行うセルフリフレ ッシュ専用回路と、高電位電源及び低電位電源に基づく 動作電源をセルフリフレッシュ専用回路に供給するため の電源回路と、検出時間よりも短い設定時間の経過を検 出したとき、高電位電源及び低電位電源間に電源回路を 接続して該電源回路に電流を流し、動作電源を出力させ るための起動手段とによりセルフリフレッシュ回路を構 成した。

【0028】また、セルフリフレッシュ専用回路は、メ モリセルアレイのメモリセルを選択する内部アドレスを 発生させるためのクロック信号を発生するオシレータと するのがよい。電源回路は高電位電源及び低電位電源間 に直列に接続された第1及び第2のトランジスタで構成 し、少なくとも第1のトランジスタは起動手段によって 導通され、第1及び第2のトランジスタ間から動作電源 を出力するようにするのがよい。

[0029]

【作用】本発明では、セルフリフレッシュ動作が開始さ れるまでの検出時間よりも短い設定時間が経過すると、 電源回路が起動されてセルフリフレッシュ専用回路に動 作電源が供給される。そのため、電源回路及びセルフリ フレッシュ専用回路における消費電流が低減される。そ して、検出時間が経過すると、セルフリフレッシュ専用 回路の動作が開始され、メモリセルアレイのセルフリフ レッシュが行われる。

[0030]

【実施例】以下、本発明をDRAMに具体化した一実施 例を図1~図3に基づいて説明する。尚、図4~6と同 様の構成については同一の符号を付してその説明を一部 省略する。

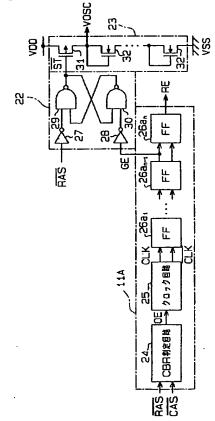

【0031】図1に示すように、本実施例のDRAM2 1は複数のメモリセルアレイSa1~San、ロウアド レスバッファ・プリデコーダ5、コラムアドレスバッフ ア・プリデコーダ6及びセルフリフレッシュ回路7Aを 備えている。DRAM21にはシステム電源から高電位 及び低電位電源VDD, VSSが供給され、DRAM21は 両電源VDD及びVSSに基づいて動作する。また、DRA M21には前記システム電源と並列にバックアップ用の バッテリ(図示略)が接続されている。システム電源が 遮断されると、バッテリからDRAM21に電源VDD, VSSが供給され、DRAM21はこの電源VDD, VSSに 基づいて動作する。

【0032】セルフリフレッシュ回路7AはCBR検出 回路8、MPX9,10、セルフリフレッシュモード検 出回路11A、セルフリフレッシュ専用回路としてのセ ルフリフレッシュ用オシレータ12、CBR用カウンタ 13、ラッチ22及びセルフリフレッシュ用のオシレー タ電源回路23により構成されている。

【0033】モード検出回路11Aにはロウアドレスス トローブ信号(以下、単にロウ信号という)バーRAS 及びコラムアドレスストローブ信号(以下、単にコラム 信号という)バーCASが入力される。オシレータ12 には電源回路23が接続されている。

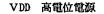

【0034】図2に示すように、モード検出回路11A はCBR判定回路24、クロック回路25、及びフリッ プフロップよりなる複数の分周器26a1~26anで 構成されている。そして、モード検出回路11Aは前記 電源VDD, VSSに基づいて動作する。

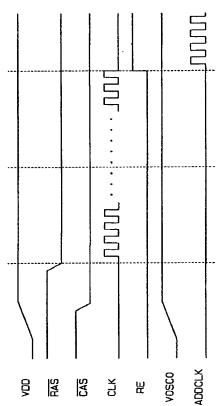

【0035】判定回路24はロウ信号バーRAS及びコ ラム信号バーCASを入力する。図3に示すように、コ ラム信号バーCASが立ち下がってからロウ信号バーR ASが立ち下がる。すると、判定回路24はHレベルの 出力許可信号OEをクロック回路25に出力する。コラ ム信号パーCAS及びロウ信号バーRASがLレベルに 保持されていると、判定回路24は出力許可信号OEを 出力し続ける。ロウ信号バーRASが立ち上がると、判 定回路24は出力許可信号OEの出力を停止する。

【0036】クロック回路25はHレベルの出力許可信 号OEに基づいて活性化され、図3に示すクロック信号 CLKを初段の分周器26a1に出力する。また、クロ ック回路25は前記クロック信号CLKを反転したクロ ック信号バーCLKを分周器26a1に出力する。

【0037】分周器26a1~26anは入力信号の周 波数を2分の1に分周し、分周した信号を次段の分周器 に出力する。そして、分周器26an-1は前記クロック 回路25がクロック信号CLKを出力し始めてから50  $\mu$ sec後にHレベルの活性化信号GEをラッチ22に 出力する。分周器26anは前記クロック回路25がク ロック信号CLKを出力し始めてから100 $\mu$ sec後 に、セルフリフレッシュを行うべく、Hレベルの検出信 号REをCBR検出回路8、オシレータ12及びMPX 9に出力する。

【0038】 ラッチ22は前記モード検出回路11Aと 共に起動手段を構成する。ラッチ22はCMOSトラン ジスタよりなるインバータ27,28と、NAND回路 29,30とで構成されたフリップフロップである。N AND回路29の一方の入力端子にはインバータ27を 介して前記ロウ信号バーRASが入力され、他方の入力 端子にはNAND回路30の出力信号が入力されてい

る。NAND回路30の一方の入力端子にはインパータ 28を介して前記活性化信号GEが入力され、他方の入 力端子にはNAND回路29の出力信号が入力されてい る。NAND回路29は両入力信号に基づいて電源回路 23を起動するための起動信号バーSTを出力する。

【0039】従って、ロウ信号パーRASがHレベルの とき、NAND回路30の出力信号に関係なく、起動信 号パーSTはHレベルとなる。また、ロウ信号パーRA SがLレベルのとき、活性化信号GEがHレベルになる と、起動信号パーSTはLレベルとなる。ロウ信号パー RASがLレベルの期間、NAND回路30の出力信号 に関係なく、起動信号パーSTはLレベルに保持され る。

【0040】電源回路23は第1のトランジスタとして のPMOSトランジスタ31及び第2のトランジスタと しての複数のNMOSトランジスタ32からなる。トラ ンジスタ31及び複数のトランジスタ32は電源VDD及 びVSS間に直列に接続されている。トランジスタ31の ゲートには前記起動信号パーSTが印加されている。各 トランジスタ32のゲートはそのドレインに接続されて いる。電源回路23はトランジスタ31のドレインから 動作電源としてのオシレータ電源Vosc をオシレータ1 2に出力する。

【0041】従って、起動信号バーSTがHレベルであ ると、トランジスタ31はオンせず、電源回路23は電 源VSSのレベルを出力する。逆に、起動信号バーSTが レレベルであると、トランジスタ31がオンするととも に、すべてのトランジスタ32がオンする。その結果、 図3に示すように、オシレータ電源Vosc が立ち上が り、電源回路23は電源VDDよりもトランジスタ31の しきい値電圧だけ低いレベルのオシレータ電源Vosc を 出力する。

【0042】このオシレータ電源 Vosc に基づいてオシ レータ12は動作可能となる。そして、モード検出回路 11AからHレベルの検出信号REが入力されると、オ シレータ12は活性化され、オシレータ電源 Vosc に基 づいて内部アドレスを発生するための所定周波数のクロ ック信号ADDCLKを出力する。

【0043】さて、システム電源が供給されると、図3 に示すように、電源VDDが立ち上がりる。システム電源 が遮断されると、DRAM21への電源VDDの供給は前 記パッテリによって行われ、電源VDDは立ち上がった状態に保持される。

【0044】コラム信号バーCASが立ち下がってから ロウ信号バーRASが立ち下がると、モード検出回路1 1Aは内部クロック信号CLKに基づいて経過時間を計 測する。コラム信号バーCAS及びロウ信号バーRAS がローレベルのまま50µsec経過すると、モード検 出回路11AはHレベルの活性化信号GEをラッチ22 に出力する。

【0045】このとき、ラッチ22にはLレベルのロウ 信号バーRASが入力されているため、起動信号バーS TはLレベルとなる。ロウ信号バーRASがLレベルの 期間、起動信号バーSTはLレベルに保持される。

【0046】このLレベルの起動信号バーSTに基づい て電源回路23のトランジスタ31及びすべてのトラン ジスタ32がオンし、オシレータ電源Vosc が立ち上が り、この電源Vosc がオシレータ12に出力される。こ のオシレータ電源Vosc に基づいてオシレータ12は動 作可能となる。

【0047】そして、コラム信号バーCAS及びロウ信 号パーRASがローレベルのまま100 $\mu$ sec(活性 化信号GEの出力から50 $\mu$ sec)経過すると、モー ド検出回路11Aはセルフリフレッシュを行うべく、H レベルの検出信号REをCBR検出回路8、オシレータ 12及びMPX9に出力する。

【0048】この検出信号REによってオシレータ12 は活性化され、オシレータ電源Vosc に基づいて内部ア ドレスを発生させるための所定周波数のクロック信号A DDCLKを出力する。MPX9はクロック信号ADD CLKを入力し、内部信号バーRAS1としてバッファ ・プリデコーダ5及びCBR検出回路8に出力する。 【0049】そして、内部信号バーRAS1の立ち下が りがバッファ・プリデコーダ5に入力されると、バッフ ァ・プリデコーダ5が活性化される。一方、内部信号バ ーRAS1の立ち下がりがCBR検出回路8に入力され ると、CBR検出回路8はカウントアップ信号CEをカ ウンタ13に出力する。

【0050】 カウンタ13はカウントアップ信号CEに 基づいてアドレスをアップカウントし、カウント値CV をMPX10に出力する。MPX10はカウント値CV をアドレス信号IRAとしてパッファ・プリデコーダ5 に出力する。

【0051】すると、バッファ・プリデコーダ5はアド レス信号IRAに基づくプリデコード信号DRAを各デ コーダ2に出力する。各デコーダ2はデコード信号DR Aを選択信号にデコードしその選択信号に基づいて各セ ルアレイSA1~SAnの所定のワード線を選択する。

選択されたワード線に接続されるセルのデータはセンス ・アンプ3によって増幅され、そのデータは再びセルに 書き込まれる。尚、バッファ・プリデコーダ5は内部信 号バーRAS1の立ち上がりが入力されると非活性化さ れる。

【0052】そして、再び内部信号バーRAS1の立ち 下がりがバッファ・プリデコーダ5及びCBR検出回路 8に入力されると、バッファ・プリデコーダ5が活性化 される。また、CBR検出回路8はカウントアップ信号 CEをCBR用カウンタ13に出力する。そのため、C BR用カウンタ13はアドレスを更にアップカウント し、そのカウント値CVをMPX10を介してアドレス 信号1RAとしてバッファ・プリデコーダ5に出力す る。

【0053】すると、バッファ・プリデコーダ5はアド レス信号IRAに基づいたプリデコード信号DRAを各 デコーダ2に出力する。各デコーダ2はプリデコード信 号DRAを選択信号にデコードしその選択信号に基づい て各セルアレイSA1~SAnの所定のワード線を選択 する。選択されたワード線に接続されるセルのデータは センスアンプ3によって増幅され、そのデータは再びセ ルに書き込まれる。

【0054】以下、オシレータ12から出力される内部 信号パーIRASの立ち下がり毎に、前記と同様にして 各セルアレイSa1~Sanの異なるワード線が順次選 択され、その選択されたワード線に接続されたセルのセ ルフリフレッシュが行われる。

【0055】このように、本実施例では セルフリフレ ッシュの開始までの検出時間(100µsec)が経過 する以前に、それよりも短い設定時間(50µsec) 経過したときに、電源回路23が起動される。そして、 電源回路23によってオシレータ電源Vosc がオシレー タ12に供給される。そのため、電源回路23及びオシ レータ12における消費電流を低減することができる。 また、このときロウ信号バーRASがLレベルであるため、電源回路23の消費電流はセルフリフレッシュ動作 に関係のないスタンバイ電流とはならない。

【0056】なお、本実施例において、活性化信号GE の出力タイミングは、クロック回路25からクロック信 号CLKが出力され始めてから100 $\mu$ sec経過する 以前にオシレータ電源Voscが立ち上がっているように 設定されればよい。例えば、分周器26an-1の前段の 分周器26an-2 (図示略)の出力信号を活性化信号G Eとし、クロック信号CLKが出力され始めてから25  $\mu$ sec経過後に、Hレベルの活性化信号GEが出力さ れるようにしてもよい。

【0057】また、本実施例では、電源VDD, VSSに基 づいてDRAM21を動作させるようにしたが、電源V DDを昇圧又は降圧した内部電源VIと電源VSSとに基づ いてDRAM21を動作させるように構成してもよい。 【0058】

【発明の効果】以上詳述したように、本発明によれば、 セルフリフレッシュ動作のみに関係する回路を、セルフ リフレッシュ動作に間に合うように動作させることによ り、消費電流を低減することができる。

【図面の簡単な説明】

【図1】本発明を具体化した一実施例の半導体記憶装置 の電気的構成を示すブロック図である。

(図2)図1のモード検出回路、ラッチ及びオシレータ 電源回路の詳細を示す回路図である。

【図3】図1の半導体記憶装置におけるセルフリフレッシュ動作を示すタイムチャートである。

【図4】従来の半導体記憶装置の電気的構成を示すプロ ック図である。

【図5】図4のオシレータ電源回路の一例を示す回路図 である。

【図6】図4の半導体記憶装置におけるセルフリフレッ シュ動作を示すタイムチャートである。

【符号の説明】

7A セルフリフレッシュ回路

11A モード検出回路及び起動手段としてのセルフリ フレッシュモード検出回路

12 セルフリフレッシュ専用回路としてのセルフリフ レッシュ用オシレータ

22 起動手段としてのラッチ

23 電源回路としてのセルフリフレッシュ用オシレー タ電源回路

31 第1のトランジスタとしてのPMOSトランジス タ

32 第2のトランジスタとしてのNMOSトランジス

タ

バーCAS コラムアドレスストローブ信号

バーRAS ロウアドレスストロープ信号

SA1~SAn メモリセルアレイ

Vosc 動作電源としてのオシレータ電源

【図1】

VSS 低電位電源

本発明を具体化した一実施例の半導体記憶装置の電気的構成を示すブロック図 2 RAS o Š۷ ک N ХdУ ロウアドレスバッファ ・プリデューダ ORA メモリセル プレイ 00 · J - - 6 セルフリフレッシュ用 オシレータ電源回路 セルフリフレッシュ用 SB ADOCI VOSC ļ ך נו t77 m, ដ្ ິດ . . . . ラッチ 11A 4 コラム デコータ セルフリフレッシュ は日田であり 쁊 ц, SA, ÇAS ល្ 0 ~57 4-57-60 メホリセル プレイ 0 ¥ Q₀-МΡХ **д8** п77 кил IRA 477 777 **CB日用** カウンタ m Im S . . . . 2547FVX X+77. Y152-9 DCA ゴラム デコーダ 4 ω

図1のモード検出回路、ラッチ及びオシレータ電源回路の詳録を示す回路図

· · ·

【図6】

\* · • ·

.

## 図4のオシレータ電源目站の一例を示す目路図

## 図4の半導体記憶装置におけるセルフリフレッシュ動作を示すタイムチャート